End-to-End RTL to GDSII flow for digital clock circuit

Abstract:

This project presents the design and implementation of a Digital Clock Circuit through a fully automated RTL-to-GDSII flow. The circuit performs precise timekeeping with features such as second, minute, and hour transitions. The project covers every stage of the VLSI design process, from initial preparation to layout verification, ensuring adherence to timing, power, and area constraints. Key steps include synthesis, placement, routing, static timing analysis (STA), and post-layout validation. The final output is a clean, manufacturable layout in GDSII format, ready for fabrication.

Introduction:

The Digital Clock Circuit is a vital module for accurate timekeeping in embedded systems and modern IC designs. This project demonstrates the end-to-end design flow for such a circuit, leveraging industry-standard tools and methodologies. By following a structured process, from Register Transfer Level (RTL) coding to final GDSII layout generation, this project ensures a robust and manufacturable solution that meets strict design constraints. The flow emphasizes process optimization at each stage, ensuring a balance between performance, power, and area.

Methodology:

1. Preparation:

The preparation phase is crucial for setting up the design environment and ensuring the project begins on a solid foundation. This step involves understanding the Digital Clock Circuit’s specifications, such as the required clock transitions for seconds, minutes, and hours, and identifying the functional requirements. During this phase, technology libraries are selected based on the fabrication process, and design constraints (timing, power, and area) are defined. Design tools, such as synthesis and layout tools, are configured to match the project’s requirements. A comprehensive plan is established to streamline the flow and mitigate errors in later stages.

2. Synthesis:

Synthesis translates the high-level RTL description written in Verilog into a gate-level netlist that represents the circuit in terms of logic gates and standard cells. The process involves mapping the design to a specific standard cell library provided by the foundry. Timing constraints are applied to ensure that the synthesized netlist meets performance requirements. Optimizations are performed during synthesis to reduce the design's area and power consumption while maintaining functional correctness. The synthesized netlist is verified through functional simulations to ensure it aligns with the intended behavior of the RTL design.

3. Placement:

Placement is a two-step process involving floorplanning and standard cell placement. Floorplanning defines the layout of the chip, including the positioning of functional blocks, power grids, and input/output ports. Standard cells, which represent individual logic gates, are then automatically placed within the defined chip area. The goal is to minimize interconnect lengths and avoid routing congestion. This stage ensures efficient utilization of the chip’s area, with attention to design constraints such as power distribution and clock tree structure. Placement quality is assessed using metrics like wirelength and congestion maps.

4. Static Timing Analysis (STA):

Static Timing Analysis is performed after placement to verify that all timing constraints, such as setup and hold times, are met. This involves checking signal propagation delays along critical paths to ensure that the circuit operates reliably at the target clock frequency. Timing violations identified in this stage are addressed by adjusting constraints, optimizing cell placement, or resizing standard cells to improve performance. Pre-route STA helps ensure that the design remains robust as it progresses to the routing stage.

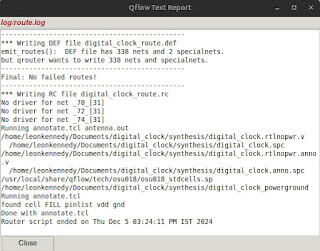

5. Routing:

Routing connects the placed standard cells with metal interconnects to complete the circuit. The process is divided into global routing and detailed routing. Global routing defines the overall paths for signals while avoiding congestion and minimizing delays. Detailed routing establishes precise connections between pins, adhering to design rules for spacing, width, and via placement. This step accounts for RC parasitics, which can impact signal timing and power consumption. Parasitic extraction is performed after routing to ensure accurate modeling for subsequent timing analysis.

6. Post-Route STA:

Post-route STA is a critical step to validate the circuit’s timing after routing has been completed. With parasitics included, this stage ensures that the interconnect delays are accurately modeled, and timing constraints are fully met. Any remaining violations, such as negative slack on critical paths, are resolved through adjustments like buffer insertion, wire sizing, or path optimization. This stage ensures that the design is fully compliant with the target clock frequency and performance specifications.

7. Migration:

The migration phase prepares the design for physical layout generation. Design files are converted into formats compatible with verification and layout tools. Special attention is given to ensure compatibility with fabrication processes. This step bridges the gap between logical design and physical implementation, creating a seamless flow for layout verification.

8. Design Rule Check (DRC):

DRC verifies that the layout adheres to manufacturing design rules provided by the foundry. These rules include constraints on wire spacing, via placement, and metal layer usage. DRC ensures that the design is manufacturable and free from defects that could arise during fabrication. Any violations are identified and corrected to maintain compliance with foundry guidelines.

9. Layout Versus Schematic (LVS):

LVS compares the final layout with the original schematic to ensure they are functionally equivalent. This step verifies that all connections in the layout match the netlist generated during synthesis. LVS identifies and resolves discrepancies such as missing connections, shorts, or extra elements, ensuring the layout accurately reflects the intended design.

10. GDSII Generation:

GDSII generation is the final step in the RTL-to-GDSII flow. The layout, verified and cleaned of any errors, is converted into the industry-standard GDSII format, which is used for fabrication. This file contains all the information about the circuit’s physical layout, including cell placement, interconnects, and metal layers. It is the final deliverable sent to the foundry for tape-out.

11. Clean-Up:

The clean-up phase ensures that the design environment is organized and free of unnecessary files or redundant configurations. Project files, including scripts, netlists, and layouts, are archived systematically for future reference. Documentation summarizing the design process, challenges, and results is prepared, providing a complete overview of the project for stakeholders and team members.

Conclusion:

This project successfully demonstrates the design and implementation of a Digital Clock Circuit using a complete RTL-to-GDSII flow. By following a systematic approach from preparation to GDSII generation, the project ensures a manufacturable design that balances timing, power, and area requirements. This workflow can be extended to other digital circuits for reliable and efficient VLSI design.

Verilog code snippet:

module digital_clock(

input wire clk, // 1 Hz clock input

input wire reset, // Reset signal

output reg [5:0] seconds, // 0 to 59

output reg [5:0] minutes, // 0 to 59

output reg [4:0] hours // 0 to 23

);

// Clock behavior

always @(posedge clk or posedge reset) begin

if (reset) begin

seconds <= 6'b0;

minutes <= 6'b0;

hours <= 5'b0;

end else begin

// Increment seconds

if (seconds == 59) begin

seconds <= 0;

// Increment minutes

if (minutes == 59) begin

minutes <= 0;

// Increment hours

if (hours == 23) begin

hours <= 0;

end else begin

hours <= hours + 1;

end

end else begin

minutes <= minutes + 1;

end

end else begin

seconds <= seconds + 1;

end

end

end

endmodule

References:

Weste, N. H. E., & Harris, D. M. "CMOS VLSI Design: A Circuits and Systems Perspective."

Cadence/ASIC Tools Documentation for RTL-to-GDSII Flow.

Industry standard documents on DRC and LVS techniques.

.pdf.png)

Comments

Post a Comment